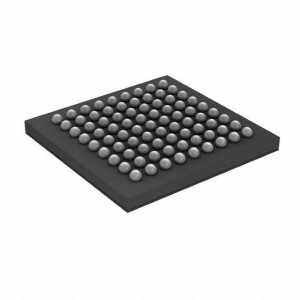

TMS320VC5509AZAY Processeurs et contrôleurs de signal numérique – DSP, DSC Processeur de signal numérique à virgule fixe 179-NFBGA -40 à 85

♠ Description du produit

| Attribut de produit | Valeur d'attribut |

| Fabricant: | Texas Instruments |

| Catégorie de produit: | Processeurs et contrôleurs de signaux numériques - DSP, DSC |

| RoHS : | Détails |

| Produit: | DSP |

| Série: | TMS320VC5509A |

| Style de montage : | CMS/CMS |

| Paquet/boîte : | NFBGA-179 |

| Cœur: | C55x |

| Nombres de coeurs: | 1 noyau |

| Fréquence d'horloge maximale : | 200 MHz |

| Mémoire d'instructions du cache L1 : | - |

| Mémoire de données du cache L1 : | - |

| Taille de la mémoire programme : | 64 Ko |

| Taille de la RAM de données : | 256 ko |

| Tension d'alimentation de fonctionnement : | 1,6V |

| Température de fonctionnement minimale : | - 40 C |

| Température de fonctionnement maximale : | + 85 C |

| Emballage: | Plateau |

| Marque: | Texas Instruments |

| Type d'instruction : | Un point fixe |

| Type d'interface : | I2C |

| Sensible à l'humidité : | Oui |

| Type de produit: | DSP - Processeurs et contrôleurs de signaux numériques |

| Quantité de l'emballage d'usine : | 160 |

| Sous-catégorie : | Processeurs et contrôleurs intégrés |

| Tension d'alimentation - Max : | 1,65V |

| Tension d'alimentation - Min : | 1,55V |

| Minuteries de chien de garde : | Minuterie de chien de garde |

♠ Processeur de signal numérique à virgule fixe TMS320VC5509A

Le processeur de signal numérique (DSP) à virgule fixe TMS320VC5509A est basé sur le cœur de processeur CPU de génération DSP TMS320C55x.L'architecture DSP C55x™ atteint des performances élevées et une faible consommation grâce à un parallélisme accru et à une concentration totale sur la réduction de la dissipation de puissance.Le CPU prend en charge une structure de bus interne composée d'un bus de programme, de trois bus de lecture de données, de deux bus d'écriture de données et de bus supplémentaires dédiés à l'activité périphérique et DMA.Ces bus offrent la possibilité d'effectuer jusqu'à trois lectures de données et deux écritures de données en un seul cycle.En parallèle, le contrôleur DMA peut effectuer jusqu'à deux transferts de données par cycle indépendamment de l'activité du CPU.

Le processeur C55x fournit deux unités de multiplication-accumulation (MAC), chacune capable de multiplier 17 bits x 17 bits en un seul cycle.Une unité arithmétique/logique (ALU) centrale de 40 bits est prise en charge par une ALU 16 bits supplémentaire.L'utilisation des ALU est sous contrôle du jeu d'instructions, ce qui permet d'optimiser l'activité parallèle et la consommation d'énergie.Ces ressources sont gérées dans l'unité d'adresse (AU) et l'unité de données (DU) de la CPU C55x.

La génération C55x DSP prend en charge un jeu d'instructions à largeur d'octet variable pour une densité de code améliorée.L'unité d'instruction (IU) effectue des extractions de programme 32 bits à partir de la mémoire interne ou externe et met en file d'attente les instructions pour l'unité de programme (PU).L'unité de programme décode les instructions, dirige les tâches vers les ressources AU et DU et gère le pipeline entièrement protégé.La capacité de branchement prédictive évite les vidages de pipeline lors de l'exécution d'instructions conditionnelles.

Les fonctions d'entrée et de sortie à usage général et l'A/D 10 bits fournissent suffisamment de broches pour l'état, les interruptions et les E/S de bit pour les écrans LCD, les claviers et les interfaces multimédias.L'interface parallèle fonctionne selon deux modes, soit en tant qu'esclave d'un microcontrôleur utilisant le port HPI, soit en tant qu'interface média parallèle utilisant l'EMIF asynchrone.Le support série est pris en charge par deux périphériques MultiMedia Card/Secure Digital (MMC/SD) et trois McBSP.

L'ensemble de périphériques 5509A comprend une interface de mémoire externe (EMIF) qui fournit un accès sans colle aux mémoires asynchrones telles que EPROM et SRAM, ainsi qu'aux mémoires haute vitesse et haute densité telles que la DRAM synchrone.Les périphériques supplémentaires incluent le bus série universel (USB), l'horloge en temps réel, la minuterie de surveillance, l'interface multi-maître et esclave I2C.Trois ports série à mémoire tampon multicanal en duplex intégral (McBSP) fournissent une interface sans colle à une variété de périphériques série standard de l'industrie et une communication multicanal avec jusqu'à 128 canaux activés séparément.L'interface hôte-port améliorée (HPI) est une interface parallèle 16 bits utilisée pour fournir au processeur hôte un accès à 32 Ko de mémoire interne sur le 5509A.Le HPI peut être configuré en mode multiplexé ou non multiplexé pour fournir une interface sans colle à une grande variété de processeurs hôtes.Le contrôleur DMA assure le déplacement des données pour six contextes de canaux indépendants sans intervention de l'unité centrale, fournissant un débit DMA allant jusqu'à deux mots de 16 bits par cycle.Deux temporisateurs à usage général, jusqu'à huit broches d'E/S à usage général (GPIO) dédiées et la génération d'horloge à boucle à verrouillage de phase numérique (DPLL) sont également inclus.

Le 5509A est pris en charge par le eXpressDSP™ primé du secteur, l'environnement de développement intégré (IDE) Code Composer Studio™, le DSP/BIOS™, la norme d'algorithme de Texas Instruments et le plus grand réseau tiers du secteur.L'IDE Code Composer Studio comprend des outils de génération de code, notamment un compilateur C et un éditeur de liens visuel, un simulateur, des pilotes de périphérique d'émulation RTDX™, XDS510™ et des modules d'évaluation.Le 5509A est également pris en charge par la bibliothèque DSP C55x qui comprend plus de 50 noyaux logiciels fondamentaux (filtres FIR, filtres IIR, FFT et diverses fonctions mathématiques) ainsi que des bibliothèques de prise en charge de puces et de cartes.

Le cœur DSP TMS320C55x a été créé avec une architecture ouverte qui permet l'ajout de matériel spécifique à l'application pour améliorer les performances sur des algorithmes spécifiques.Les extensions matérielles du 5509A offrent un équilibre parfait entre les performances des fonctions fixes et la flexibilité programmable, tout en obtenant une faible consommation d'énergie et un coût traditionnellement difficile à trouver sur le marché des processeurs vidéo.Les extensions permettent au 5509A d'offrir des performances de codec vidéo exceptionnelles avec plus de la moitié de sa bande passante disponible pour effectuer des fonctions supplémentaires telles que la conversion de l'espace colorimétrique, les opérations d'interface utilisateur, la sécurité, TCP/IP, la reconnaissance vocale et la conversion texte-parole.En conséquence, un seul DSP 5509A peut alimenter la plupart des applications vidéo numériques portables avec une marge de traitement à revendre.Pour plus d'informations, consultez la référence du programmeur des extensions matérielles TMS320C55x pour les applications image/vidéo (numéro de documentation SPRU098).Pour plus d'informations sur l'utilisation de la bibliothèque de traitement d'images DSP, consultez la référence du programmeur de la bibliothèque de traitement d'images/vidéos TMS320C55x (numéro de documentation SPRU037).

• Processeur de signal numérique TMS320C55x™ à virgule fixe hautes performances et basse consommation

− 9.26-, 6.95-, 5-ns Temps de cycle d'instruction

− Fréquence d'horloge 108, 144, 200 MHz

− Une/Deux instruction(s) exécutée(s) par cycle

− Multiplicateurs doubles [jusqu'à 400 millions de multiplications accumulées par seconde (MMACS)]

− Deux unités arithmétiques/logiques (ALU)

− Trois bus internes de lecture de données/opérandes et deux bus internes de données/écriture d'opérandes

• RAM sur puce de 128 K x 16 bits, composée de :

− 64K octets de RAM à double accès (DARAM) 8 blocs de 4K × 16 bits

− 192K octets de RAM à accès unique (SARAM) 24 blocs de 4K × 16 bits

• 64 K octets de ROM sur puce à un état d'attente (32 K × 16 bits)

• Espace mémoire externe adressable maximal de 8 M × 16 bits (DRAM synchrone)

• Mémoire de bus parallèle externe 16 bits prenant en charge :

− Interface de mémoire externe (EMIF) avec capacités GPIO et interface sans colle pour :

− RAM statique asynchrone (SRAM)

− EPROM asynchrone

− DRAM synchrone (SDRAM)

− Interface hôte-port améliorée parallèle 16 bits (EHPI) avec capacités GPIO

• Contrôle programmable à faible consommation d'énergie de six domaines fonctionnels d'appareils

• Logique d'émulation basée sur le balayage sur puce

• Périphériques sur puce

− Deux temporisateurs 20 bits

− Minuterie de chien de garde

− Contrôleur d'accès direct à la mémoire (DMA) à six canaux

− Trois ports série prenant en charge une combinaison de :

− Jusqu'à 3 ports série tamponnés multicanaux (McBSP)

− Jusqu'à 2 interfaces de cartes numériques multimédia/sécurisées

− Générateur d'horloge de boucle à verrouillage de phase programmable

− Sept (LQFP) ou huit (BGA) broches d'E/S à usage général (GPIO) et une broche de sortie à usage général (XF)

− Port esclave USB pleine vitesse (12 Mbps) prenant en charge les transferts en masse, interrompus et isochrones

− Interface multi-maître et esclave à circuit intégré (I2C)

−Horloge en temps réel (RTC) avec entrée Crystal, domaine d'horloge séparé, alimentation électrique séparée

− Approximation A/N 4 canaux (BGA) ou 2 canaux (LQFP) 10 bits successifs

• Logique de balayage des limites IEEE Std 1149.1† (JTAG)

• Paquets:

− 144-Terminal Low-Profile Quad Flatpack (LQFP) (suffixe PGE)

− 179-Terminal MicroStar BGA™ (Ball Grid Array) (suffixe GHH)

− MicroStar BGA™ sans plomb à 179 bornes (Ball Grid Array) (suffixe ZHH)

• Noyau 1,2 V (108 MHz), 2,7 V – 3,6 VI/O

• Noyau 1,35 V (144 MHz), 2,7 V – 3,6 VI/O

• Noyau 1,6 V (200 MHz), 2,7 V – 3,6 VI/O

• Système hybride, électrique et de groupe motopropulseur (EV/HEV)

– Système de gestion de batterie (BMS)

– Chargeur embarqué

– Inverseur de traction

– Convertisseur DC/DC

– Démarreur/générateur