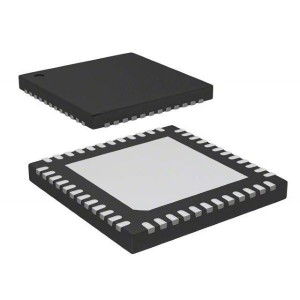

LCMXO640C-4TN144C FPGA – Réseau prédiffusé programmable sur site 640 LUTS 113 E/S

♠ Description du produit

| Attribut de produit | Valeur d'attribut |

| Fabricant: | Treillis |

| Catégorie de produit: | FPGA - Réseau prédiffusé programmable sur le terrain |

| RoHS : | Détails |

| Série: | LCMXO640C |

| Nombre d'éléments logiques : | 640 LE |

| Nombre d'E/S : | 113 E/S |

| Tension d'alimentation - Min : | 1,71 V |

| Tension d'alimentation - Max : | 3.465V |

| Température de fonctionnement minimale : | 0C |

| Température de fonctionnement maximale : | + 85 C |

| Débit de données: | - |

| Nombre d'émetteurs-récepteurs : | - |

| Style de montage : | CMS/CMS |

| Paquet/boîte : | TQFP-144 |

| Emballage: | Plateau |

| Marque: | Treillis |

| RAM distribuée : | 6,1 ko |

| Hauteur: | 1,4 mm |

| Longueur: | 20 millimètres |

| Fréquence de fonctionnement maximale : | 550 MHz |

| Sensible à l'humidité : | Oui |

| Nombre de blocs de matrice logique - LAB : | 80 LABO |

| Courant d'alimentation de fonctionnement : | 17 mA |

| Tension d'alimentation de fonctionnement : | 1,8 V/2,5 V/3,3 V |

| Type de produit: | FPGA - Réseau prédiffusé programmable sur le terrain |

| Quantité de l'emballage d'usine : | 60 |

| Sous-catégorie : | Circuits intégrés logiques programmables |

| Mémoire totale: | 6,1 ko |

| Largeur: | 20 millimètres |

| Unité de poids: | 1,319g |

Non volatile, reconfigurable à l'infini

• Allumage instantané : s'allume en quelques microsecondes

• Puce unique, aucune mémoire de configuration externe requise

• Excellente sécurité de conception, pas de flux binaire à intercepter

• Reconfigurer la logique basée sur la SRAM en quelques millisecondes

• SRAM et mémoire non volatile programmables via le port JTAG

• Prend en charge la programmation en arrière-plan de la mémoire non volatile

Mode veille

• Permet jusqu'à 100 fois la réduction du courant statique

Reconfiguration TransFR™ (TFR)

• Mise à jour de la logique sur le terrain pendant que le système fonctionne

Haute densité d'E/S à logique

• 256 à 2 280 LUT4

• 73 à 271 E/S avec de nombreuses options de package

• Migration de densité prise en charge

• Emballage sans plomb/conforme RoHS

Mémoire embarquée et distribuée

• Jusqu'à 27,6 Kbits de RAM de bloc intégrée sysMEM™

• Jusqu'à 7,7 Kbits de RAM distribuée

• Logique de contrôle FIFO dédiée

Tampon d'E/S flexible

• La mémoire tampon sysIO™ programmable prend en charge une large gamme d'interfaces :

– LVCMOS 3.3/2.5/1.8/1.5/1.2

– LVTTL

– PCI

– LVDS, Bus-LVDS, LVPECL, RSDS

PLL sysCLOCK™

• Jusqu'à deux PLL analogiques par appareil

• Multiplication, division et déphasage de l'horloge

Prise en charge au niveau du système

• Balayage des limites de la norme IEEE 1149.1

• Oscillateur intégré

• Les appareils fonctionnent avec une alimentation de 3,3 V, 2,5 V, 1,8 V ou 1,2 V

• Programmation intégrée au système conforme à la norme IEEE 1532