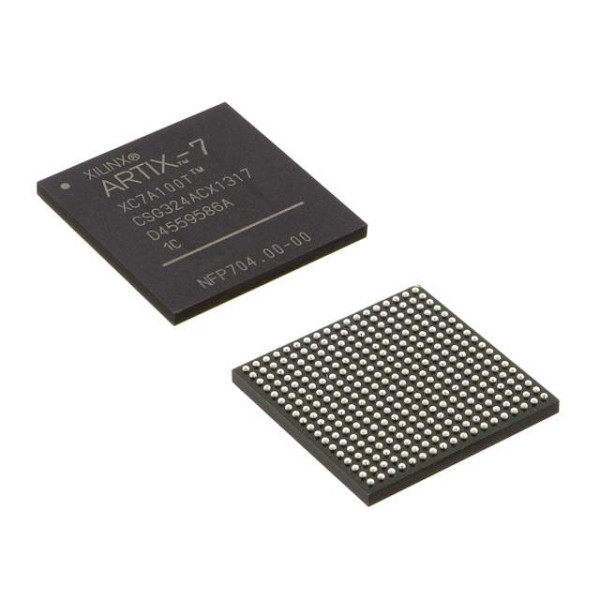

FPGA XC7A50T-2CSG324I – Réseau de portes programmables par l'utilisateur XC7A50T-2CSG324I

♠ Description du produit

| Attribut du produit | Valeur de l'attribut |

| Fabricant: | Xilinx |

| Catégorie de produit : | FPGA - Réseau de portes programmables sur site |

| Série: | XC7A50T |

| Nombre d'éléments logiques : | 52160 LE |

| Nombre d'E/S : | 210 E/S |

| Tension d'alimentation - Min : | 0,95 V |

| Tension d'alimentation - Max : | 1,05 V |

| Température minimale de fonctionnement : | - 40 °C |

| Température de fonctionnement maximale : | + 100 °C |

| Débit de données : | - |

| Nombre d'émetteurs-récepteurs : | - |

| Style de montage : | CMS/CMS |

| Emballage / Étui : | CSBGA-324 |

| Marque: | Xilinx |

| RAM distribuée : | 600 kbit |

| RAM en bloc intégrée - EBR : | 2700 kbit |

| Sensible à l'humidité : | Oui |

| Nombre de blocs de matrice logique - LAB : | 4075 LABORATOIRE |

| Tension d'alimentation de fonctionnement : | 1 V |

| Type de produit : | FPGA - Réseau de portes programmables sur site |

| Quantité du pack d'usine : | 1 |

| Sous-catégorie: | Circuits intégrés logiques programmables |

| Nom commercial : | Artix |

| Poids unitaire : | 1 oz |

♠ Les FPGA Xilinx® série 7 comprennent quatre familles de FPGA qui répondent à la gamme complète des exigences du système, allant des applications à faible coût, à petit facteur de forme, sensibles aux coûts et à volume élevé aux applications de connectivité ultra haut de gamme, à la capacité logique et à la capacité de traitement du signal pour les applications hautes performances les plus exigeantes

Les FPGA Xilinx® série 7 comprennent quatre familles de FPGA répondant à l'ensemble des besoins des systèmes, des applications économiques, compactes et à haut volume aux applications hautes performances les plus exigeantes en termes de bande passante, de capacité logique et de traitement du signal. Les FPGA série 7 comprennent :

• Famille Spartan®-7 : Optimisée pour un faible coût, une consommation d'énergie minimale et des performances d'E/S élevées. Disponible dans un boîtier compact et économique pour un encombrement PCB minimal.

• Famille Artix®-7 : Optimisée pour les applications basse consommation nécessitant des émetteurs-récepteurs série et un débit DSP et logique élevé. Offre le coût total de nomenclature le plus bas pour les applications à haut débit et sensibles aux coûts.

• Famille Kintex®-7 : optimisée pour un meilleur rapport prix-performances avec une amélioration de 2X par rapport à la génération précédente, permettant une nouvelle classe de FPGA.

• Famille Virtex®-7 : optimisée pour des performances et une capacité système maximales, avec une amélioration de 2 fois des performances système. Des appareils aux capacités les plus élevées grâce à la technologie SSI (Stacked Silicon Interconnect).

Construits sur une technologie de processus de pointe, haute performance, basse consommation (HPL), 28 nm, à grille métallique haute k (HKMG), les FPGA de la série 7 permettent une augmentation inégalée des performances du système avec 2,9 Tb/s de bande passante d'E/S, 2 millions de capacité de cellules logiques et 5,3 TMAC/s DSP, tout en consommant 50 % d'énergie en moins que les appareils de la génération précédente pour offrir une alternative entièrement programmable aux ASSP et ASIC.

• Logique FPGA hautes performances avancée basée sur une véritable technologie de table de consultation à 6 entrées (LUT) configurable en tant que mémoire distribuée.

• RAM bloc double port de 36 Ko avec logique FIFO intégrée pour la mise en mémoire tampon des données sur puce.

• Technologie SelectIO™ hautes performances avec prise en charge des interfaces DDR3 jusqu'à 1 866 Mb/s.

• Connectivité série haut débit avec émetteurs-récepteurs multi-gigabits intégrés de 600 Mb/s à des débits maximum de 6,6 Gb/s jusqu'à 28,05 Gb/s, offrant un mode basse consommation spécial, optimisé pour les interfaces puce à puce.

• Une interface analogique configurable par l'utilisateur (XADC), intégrant deux convertisseurs analogique-numérique 12 bits 1 MSPS avec capteurs thermiques et d'alimentation intégrés.

• Tranches DSP avec multiplicateur 25 x 18, accumulateur 48 bits et pré-additionneur pour un filtrage haute performance, y compris un filtrage à coefficient symétrique optimisé.

• Tuiles de gestion d'horloge puissantes (CMT), combinant des blocs de gestion d'horloge à boucle à verrouillage de phase (PLL) et à mode mixte (MMCM) pour une haute précision et une faible gigue.

• Déployez rapidement le traitement intégré avec le processeur MicroBlaze™.

• Bloc intégré pour PCI Express® (PCIe), pour des conceptions de ports racine et de points de terminaison Gen3 jusqu'à x8.

• Grande variété d'options de configuration, y compris la prise en charge des mémoires standard, le cryptage AES 256 bits avec authentification HMAC/SHA-256 et la détection et la correction SEU intégrées.

• Boîtier flip-chip à puce nue, économique, à liaison filaire et à haute intégrité du signal, facilitant la migration entre les composants d'une même famille. Tous les boîtiers sont disponibles sans plomb et certains boîtiers avec option plomb.

• Conçu pour des performances élevées et une consommation d'énergie minimale avec un processus 28 nm, HKMG, HPL, une technologie de processus de tension de cœur de 1,0 V et une option de tension de cœur de 0,9 V pour une consommation d'énergie encore plus faible.