TMS320C6674ACYPA Multicore Fix/Float Pt Dig Sig Proc

♠ Description du produit

| Attribut du produit | Valeur de l'attribut |

| Fabricant: | Texas Instruments |

| Catégorie de produit : | Processeurs et contrôleurs de signaux numériques (DSP, DSC) |

| Produit: | DSP |

| Série: | TMS320C6674 |

| Style de montage : | CMS/CMS |

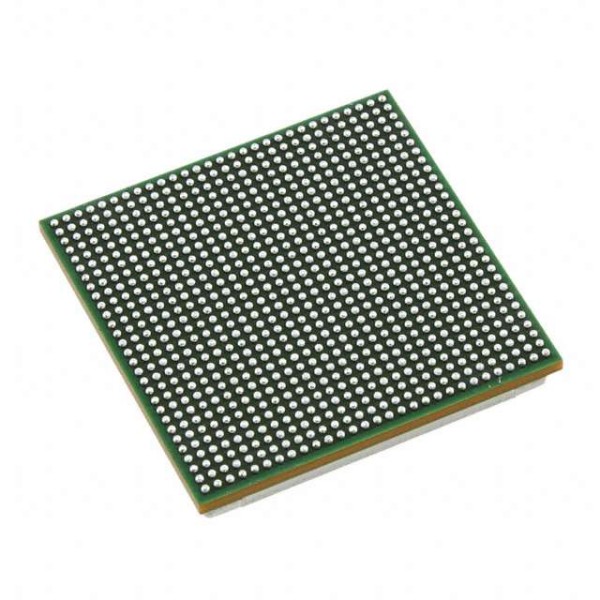

| Emballage / Étui : | FCBGA-841 |

| Cœur: | C66x |

| Nombre de cœurs : | 4 cœurs |

| Fréquence d'horloge maximale : | 1 GHz, 1,25 GHz |

| Mémoire d'instructions du cache L1 : | 4 x 32 Ko |

| Mémoire cache de données L1 : | 4 x 32 Ko |

| Taille de la mémoire du programme : | - |

| Taille de la RAM de données : | - |

| Tension d'alimentation de fonctionnement : | 900 mV à 1,1 V |

| Température minimale de fonctionnement : | - 40 °C |

| Température de fonctionnement maximale : | + 100 °C |

| Conditionnement: | Plateau |

| Marque: | Texas Instruments |

| Largeur du bus de données : | 8 bits/16 bits/32 bits |

| Type d'instruction : | virgule fixe/flottante |

| MMACS : | 160 000 MMAC |

| Sensible à l'humidité : | Oui |

| Nombre d'E/S : | 16 E/S |

| Nombre de temporisateurs/compteurs : | 12 Minuterie |

| Type de produit : | DSP - Processeurs et contrôleurs de signaux numériques |

| Quantité du pack d'usine : | 44 |

| Sous-catégorie: | Processeurs et contrôleurs intégrés |

| Tension d'alimentation - Max : | 1,1 V |

| Tension d'alimentation - Min : | 900 mV |

| Poids unitaire : | 0,173396 oz |

♠ Processeur de signal numérique multicœur à virgule fixe et flottante

Le DSP TMS320C6674 est un DSP à virgule fixe/flottante ultra-performant basé sur l'architecture multicœur KeyStone de TI. Intégrant le nouveau cœur DSP innovant C66x, ce composant peut fonctionner à une fréquence de cœur allant jusqu'à 1,25 GHz. Pour les développeurs d'applications variées, telles que les systèmes critiques, l'imagerie médicale, les tests et l'automatisation, et d'autres applications exigeant des performances élevées, le DSP TMS320C6674 de TI offre une fréquence de 5 GHz cumulée et constitue une plateforme économe en énergie et facile à utiliser. De plus, il est entièrement rétrocompatible avec tous les DSP à virgule fixe et flottante de la gamme C6000.

L'architecture KeyStone de TI offre une plateforme programmable intégrant divers sous-systèmes (cœurs C66x, sous-système mémoire, périphériques et accélérateurs). Elle utilise plusieurs composants et techniques innovants pour optimiser la communication intra-appareil et inter-appareils, permettant ainsi aux différentes ressources DSP de fonctionner efficacement et en toute fluidité. Au cœur de cette architecture se trouvent des composants clés tels que Multicore Navigator, qui assure une gestion efficace des données entre les différents composants de l'appareil. TeraNet est une matrice de commutation non bloquante permettant un transfert de données interne rapide et sans contention. Le contrôleur de mémoire partagée multicœur permet d'accéder directement à la mémoire partagée et externe sans solliciter la capacité de la matrice de commutation.

• Quatre sous-systèmes de base DSP TMS320C66x™ (C66x CorePacs), chacun avec

– Cœur de processeur à virgule fixe/flottante C66x de 1,0 GHz ou 1,25 GHz

› 40 GMAC/cœur pour point fixe à 1,25 GHz

› 20 GFLOP/cœur pour virgule flottante à 1,25 GHz

- Mémoire

› 32 Ko L1P par cœur

› 32 Ko L1D par cœur

› 512 Ko de mémoire L2 locale par cœur

• Contrôleur de mémoire partagée multicœur (MSMC)

– Mémoire SRAM MSM de 4 096 Ko partagée par quatre CorePacs DSP C66x

– Unité de protection de mémoire pour MSM SRAM et DDR3_EMIF

• Navigateur multicœur

– 8192 files d'attente matérielles polyvalentes avec gestionnaire de files d'attente

– DMA basé sur les paquets pour des transferts sans surcharge

• Coprocesseur réseau

– Packet Accelerator permet la prise en charge de

› Plan de transport IPsec, GTP-U, SCTP, PDCP

› Plan utilisateur L2 PDCP (RoHC, chiffrement aérien)

› Débit filaire de 1 Gbit/s à 1,5 mégapaquets par seconde

– Le moteur d'accélération de sécurité permet la prise en charge de

› Sécurité IPSec, SRTP, 3GPP, interface aérienne WiMAX et SSL/TLS

› ECB, CBC, CTR, F8, A5/3, CCM, GCM, HMAC, CMAC, GMAC, AES, DES, 3DES, Kasumi, SNOW 3G, SHA-1, SHA-2 (hachage 256 bits), MD5

› Vitesse de cryptage jusqu'à 2,8 Gbit/s

• Périphériques

– Quatre voies du SRIO 2.1

› Opération 1,24/2,5/3,125/5 GBaud prise en charge par voie

› Prend en charge les E/S directes et le passage de messages

› Prend en charge quatre configurations de liaison 1×, deux 2×, une 4× et deux 1× + une 2×

– PCIe Gen2

› Port unique prenant en charge 1 ou 2 voies

› Prend en charge jusqu'à 5 Gobauds par voie

– Hyperlien

› Prend en charge les connexions à d'autres périphériques d'architecture KeyStone, offrant ainsi une évolutivité des ressources

› Prend en charge jusqu'à 50 Gbauds

– Sous-système de commutation Gigabit Ethernet (GbE)

› Deux ports SGMII

› Prend en charge le fonctionnement 10/100/1000 Mbps

– Interface DDR3 64 bits (DDR3-1600)

› Espace mémoire adressable de 8 Go

– EMIF 16 bits

– Deux ports série de télécommunications (TSIP)

› Prend en charge 1024 DS0 par TSIP

› Prend en charge 2/4/8 voies à 32,768/16,384/8,192 Mbps par voie

– Interface UART

– Interface I²C

– 16 broches GPIO

– Interface SPI

– Module Sémaphore

– Douze minuteries 64 bits

– Trois PLL sur puce

• Température commerciale :

– 0°C à 85°C

• Température étendue :

– -40°C à 100°C

• Systèmes critiques pour la mission

• Systèmes de calcul haute performance

• Communications

• Audio

• Infrastructure vidéo

• Imagerie

• Analytique

• Réseautage

• Traitement des médias

• Automatisation industrielle

• Automatisation et contrôle des processus